#### **Handling Precautions**

All MOS devices are subject to damage from electrostatic discharge (ESD). Because the gate of a MOSFET is insulated from the channel, the input resistance is extremely high (ideally infinite). The gate leakage current, Isss, for a typical MOSFET is in the pA range, whereas the gate reverse current for a typical JFET is in the nA range. The input capacitance results from the insulated gate structure. Excess static charge can be accumulated because the input capacitance combines with the very high input resistance and can result in damage to the device.

**To avoid damage from ESD**, certain precautions should be taken when handling MOSFETs:

- **1.** Carefully remove MOSFET devices from their packaging. They are shipped in conductive foam or special foil conductive bags. Usually they are shipped with a wire ring around the leads, which is removed just prior to installing the MOSFET in a circuit.

- **2.** All instruments and metal benches used in assembly or test should be connected to earth ground (round or third prong of 110 V wall outlets).

- **3.** The assembler's or handler's wrist should be connected to a commercial grounding strap, which has a high-value series resistor for safety. The resistor prevents accidental contact with voltage from becoming lethal.

- **4.** Never remove a MOS device (or any other device, for that matter) from the circuit while the power is on.

- 5. Do not apply signals to a MOS device while the dc power supply is off.

# JFET vs. MOSFET vs. BJT

| Property           | BJT      | MOSFET | JFET   |

|--------------------|----------|--------|--------|

| Gm/l               | Best     | Worst  | Medium |

| Speed              | High     | Medium | Low    |

| Noise              | Moderate | Worst  | Best   |

| Good<br>Switch     | No       | Yes    | Yes    |

| High-Z Gate        | No       | Yes    | Yes    |

| ESD<br>Sensitivity | Less     | More   | Less   |

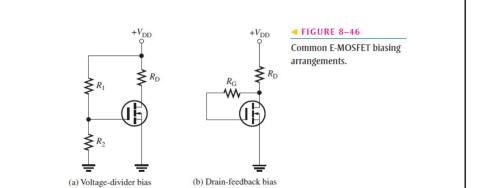

$$V_{\text{GS}} = \left(\frac{R_2}{R_1 + R_2}\right) V_{\text{DD}}$$

$$V_{\text{DS}} = V_{\text{DD}} - I_{\text{D}} R_{\text{D}}$$

**MOSFET BIASING**

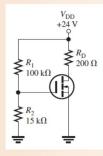

Determine  $V_{GS}$  and  $V_{DS}$  for the E-MOSFET circuit in Figure 8–47. Assume this particular MOSFET has minimum values of  $I_{D(0n)} = 200$  mA at  $V_{GS} = 4$  V and  $V_{GS(th)} = 2$  V.

► FIGURE 8-47

For the E-MOSFET in Figure 8–47, the gate-to-source voltage is

$$V_{\text{GS}} = \left(\frac{R_2}{R_1 + R_2}\right) V_{\text{DD}} = \left(\frac{15 \,\text{k}\Omega}{115 \,\text{k}\Omega}\right) 24 \,\text{V} = 3.13 \,\text{V}$$

To determine  $V_{DS}$ , first find K using the minimum value of  $I_{D(on)}$  and the specified voltage values.

$$K = \frac{I_{\text{D(on)}}}{(V_{\text{GS}} - V_{\text{GS(th)}})^2} = \frac{200 \text{ mA}}{(4 \text{ V} - 2 \text{ V})^2} = \frac{200 \text{ mA}}{4 \text{ V}^2} = 50 \text{ mA/V}^2$$

Now calculate  $I_D$  for  $V_{GS} = 3.13$  V.

$$I_D = K(V_{GS} - V_{GS(th)})^2 = (50 \text{ mA/V}^2)(3.13 \text{ V} - 2 \text{ V})^2$$

=  $(50 \text{ mA/V}^2)(1.13 \text{ V})^2 = 63.8 \text{ mA}$

Finally, calculate  $V_{\rm DS}$ .

$$V_{\rm DS} = V_{\rm DD} - I_{\rm D}R_{\rm D} = 24 \text{ V} - (63.8 \text{ mA})(200 \Omega) = 11.2 \text{ V}$$

Determine  $V_{GS}$  and  $V_{DS}$  for the circuit in Figure 8–47 given  $I_{D(on)} = 100 \text{ mA}$  at  $V_{GS} = 4 \text{ V}$  and  $V_{GS(th)} = 3 \text{ V}$ .

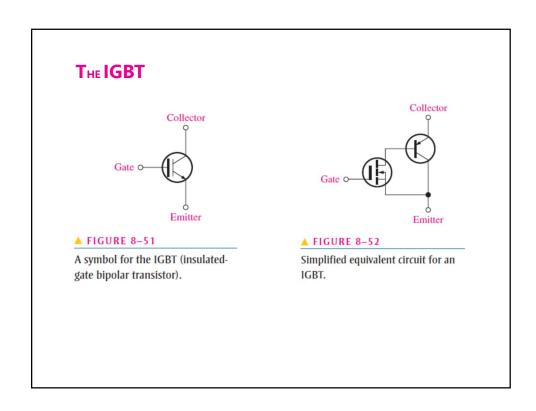

# Comparison of several device features for switching applications

| FEATURES            | IGBT    | MOSFET    | BJT      |

|---------------------|---------|-----------|----------|

| Type of input drive | Voltage | Voltage   | Current  |

| Input resistance    | High    | High      | Low      |

| Operating frequency | Medium  | High      | Low      |

| Switching speed     | Medium  | Fast (ns) | Slow(uS) |

| Saturation voltage  | Low     | High      | Low      |

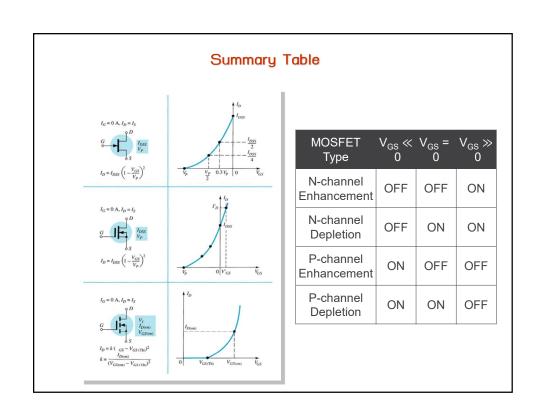

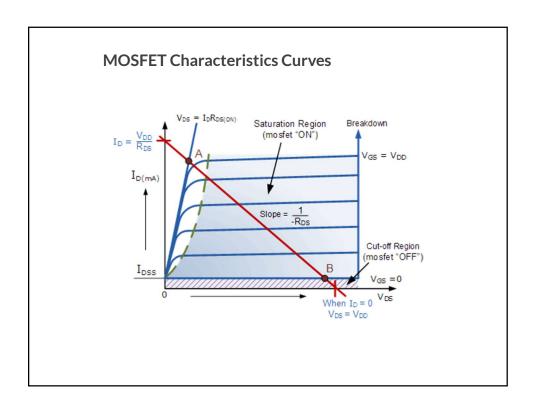

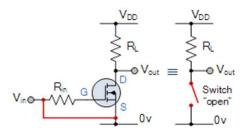

## **Cut-off Characteristics**

- •• The input and Gate are grounded ( 0V )

- ullet Gate-source voltage less than threshold voltage  $V_{GS}$  <  $V_{TH}$

- • MOSFET is "OFF" (Cut-off region)

- No Drain current flows (I<sub>D</sub> = 0 Amps)

V<sub>OUT</sub> = V<sub>DS</sub> = V<sub>DD</sub> = "1"

MOSFET operates as an "open switch"

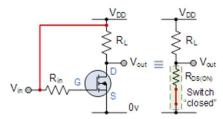

### **Saturation Characteristics**

- $\bullet \, \bullet$  The input and Gate are connected to  $V_{\text{DD}}$

- ullet Gate-source voltage is much greater than threshold voltage  $V_{GS}$  >  $V_{TH}$

- • MOSFET is "ON" (saturation region)

- • Max Drain current flows (I<sub>D</sub> = V<sub>DD</sub> / R<sub>L</sub>)

- $\bullet \bullet V_{DS} = 0V$  (ideal saturation)

- • Min channel resistance  $R_{DS(on)} < 0.1\Omega$

- $\bullet \bullet V_{OUT} = V_{DS} \cong 0.2V \text{ due to } R_{DS(on)}$

- • MOSFET operates as a low resistance "closed switch"

- Gate-source *pn* junction must be reverse-biased.

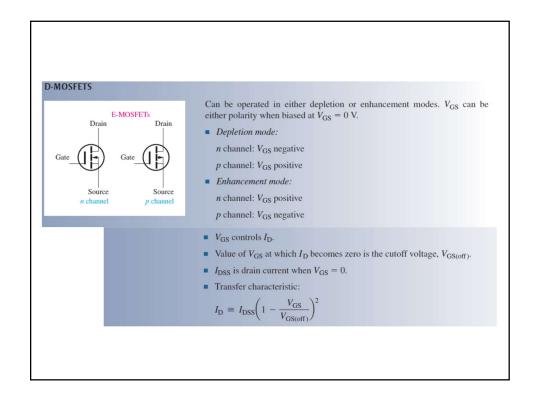

- $\blacksquare$   $V_{\rm GS}$  controls  $I_{\rm D}$ .

- Value of V<sub>DS</sub> at which I<sub>D</sub> becomes constant is the pinch-off voltage.

- Value of  $V_{GS}$  at which  $I_D$  becomes zero is the cutoff voltage,  $V_{GS(off)}$ .

- $I_{\text{DSS}}$  is drain current when  $V_{\text{GS}} = 0$ .

- Transfer characteristic:

$$I_{\rm D} \cong I_{\rm DSS} \left(1 - \frac{V_{\rm GS}}{V_{\rm GS(off)}}\right)^2$$

Forward transconductance:

$$g_m = g_{m0} \left( 1 - \frac{V_{\rm GS}}{V_{\rm GS(off)}} \right)$$

$$g_{m0} = \frac{2I_{\rm DSS}}{|V_{\rm GS(off)}|}$$