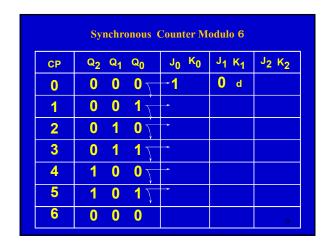

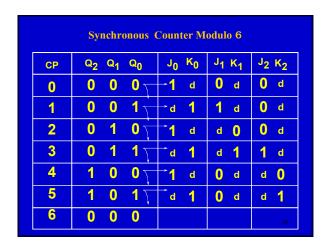

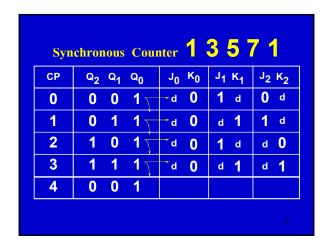

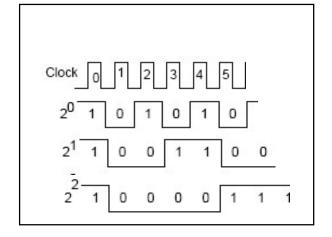

| Synchronous Counter 1 3 5 7 1 |                  |                  |                               |                               |                               |

|-------------------------------|------------------|------------------|-------------------------------|-------------------------------|-------------------------------|

| СР                            | Q <sub>2</sub> Q | 1 Q <sub>0</sub> | J <sub>0</sub> K <sub>0</sub> | J <sub>1</sub> K <sub>1</sub> | J <sub>2</sub> K <sub>2</sub> |

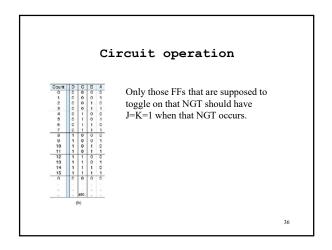

| 0                             | 0 0              | 1_               | → d <b>0</b>                  | <b>1</b> d                    | <b>0</b> d                    |

| 1                             | 0 1              | 1                | -                             |                               |                               |

| 2                             | 1 (              | 1                | <b>→</b>                      |                               |                               |

| 3                             | 1 1              | 1                | <b>→</b>                      |                               |                               |

| 4                             | 0 0              | 1                |                               |                               |                               |

|                               |                  |                  |                               |                               |                               |

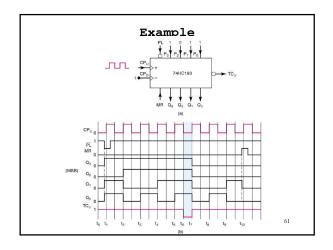

Example

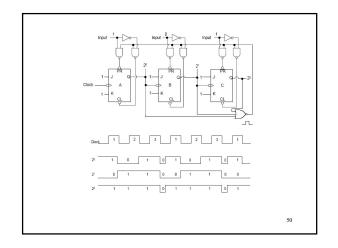

• Determine  $f_{\rm max}$  for the counter of Figure 7-17(a) if  $t_{\rm pd}$  for each FF is 50ns and  $t_{\rm pd}$  for each AND gate is 20 ns. Compare this value with  $f_{\rm max}$  for a MOD-16

• What must be done to convert this counter to MOD-32?

- Determine  $\mathbf{f}_{\text{max}}$  for the MOD-32 parallel counter.

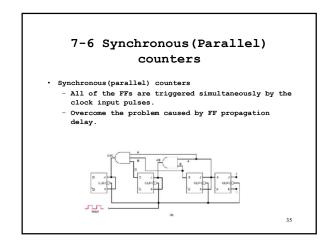

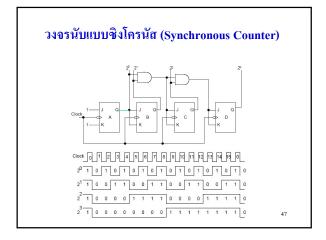

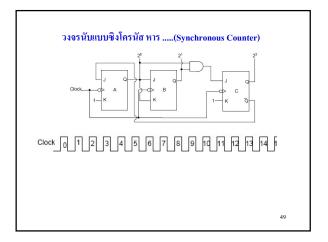

# Advantage of Synchronous counters over Asychronous

- · States are changed simultaneously.

- Total delav

- FFt $_{pd}$ +ANDgate  $t_{pd}$

- · Actual Ics

- 74ALS160/162, 74HC160/162: Synchronous decade

- 74ALS161/163, 74HC161/163: Synchronous MOD-16 counters

51

ripple counter.

- What is the advantage of a synchronous counter over an asynchronous counter? What is the disadvantage?

- How many logic devices are required for a  $\mathtt{MOD-64}$ parallel counter?

- What logic signal drives the J,K inputs of the MSB flip-flop for the counter of question 2?

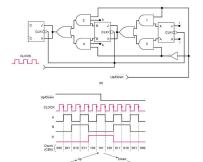

7-7 Synchronous Down and UP/Down counters

53

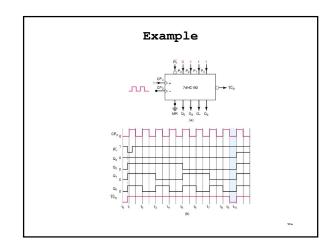

# 7-7 Synchronous Down and UP/Down counters

Example

What problems might be caused if the UP/Down signal changes levels on the NGT of the clock?

# Presettable counters

# Synchronous Presetting

- Examples of IC counters

74ALS160, 74ALS161, 74ALS612, 74ALS163

74Hc160, 74HC161, 74HC162, 74HC163

- What is meant when we say that a counter is presentable?

- Describe the difference between asynchronous and synchronous presetting.

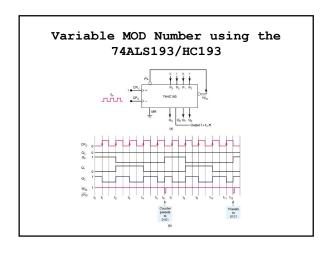

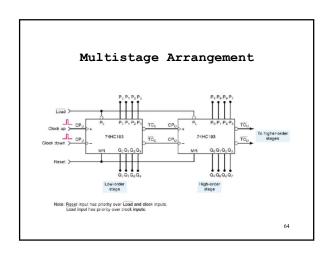

The 74ALS193/HC193 Count-up clock input (active rising edge) Count-down clock input (active rising edge) Asynchronous master reset input (active HIGH) PL Parallel data inputs P<sub>0</sub>-P<sub>3</sub>  $Q_0$ - $Q_3$ Flip-flop outputs Mode Select Terminal count-down (borrow) output (active LOW)  $\overline{\text{TC}}_{\text{D}}$ TCU Terminal count-up (carry) output (active) LOW (b)

- Describe the function of the input PL and  $\mathbf{P}_0$  to  $\mathbf{P}_3$ .

- Describe the function of the MR input

- True or False: The 74HC193 cannot be preset while MR is active.

- What logic levels must be present at  $\text{CP}_{\text{D}}, \ \text{PL}$  and MR in order for the 74ALS193 to count pulses that appear at  $\text{CP}_{\text{D}}?$

- What would be the maximum counting range for a fourstage counter made up of 74HC193 Ics?

65

### 7-11 Decoding a counter

- · Mentally decoding the binary states of the LEDs

- Becomes inconvenient as the size of the counter increases

- · Electronically decoding

- To control the timing or sequencing of operations automatically without human intervention.

- Active-High Decoding

- Active-Low Decoding

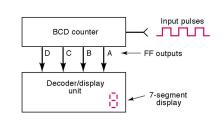

- BCD counter decoding

66

# Active-High Decoding

67

# Example

How many AND gates are required to decode completely all of the states of a MOD-32 binary counter? What are the inputs to the gate that decodes for the count of 21?

68

# Active-LOW Decoding

# BCD Counter Decoding

- How many gates are needed to decode a six-bit counter fully?

- Describe the decoding gate needed to produce a LOW output when a MOD-64 counter is at the counter of 23.

71

# 7-12 Decoding Glitches Total Decoding Glitches Total Decoding Glitches

Strobing

Review Questions

- Explain why the decoding gates for an asynchronous counter may have glitches on their outputs.

- How does strobing eliminate decoding glitches?

74

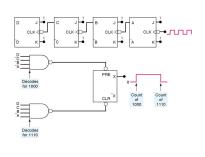

Cascading BCD counters

75

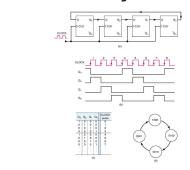

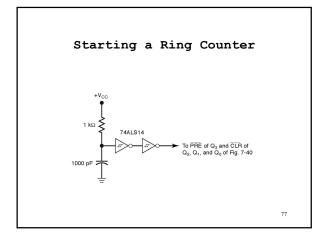

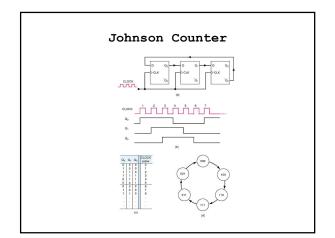

7-15 Shift-Register Counters

# Decoding A Johnson Counter

# Review Questions

- Which shift-register counter requires the most FFs for a

- given MOD number?

Which shift-register counter requires the most decoding circuitry?

- How can a ring counter be converted to a Johnson counter?

- True or False:

The outputs of a ring counter are always square waves.

- The decoding circuitry for a Johnson counter is simpler than for a binary counter

Ring and Johnson counters are synchronous counters.

- How many FFs are needed in a MOD-16 ring counter? How many are needed in a MOD-16 Johnson Counter?